The Product

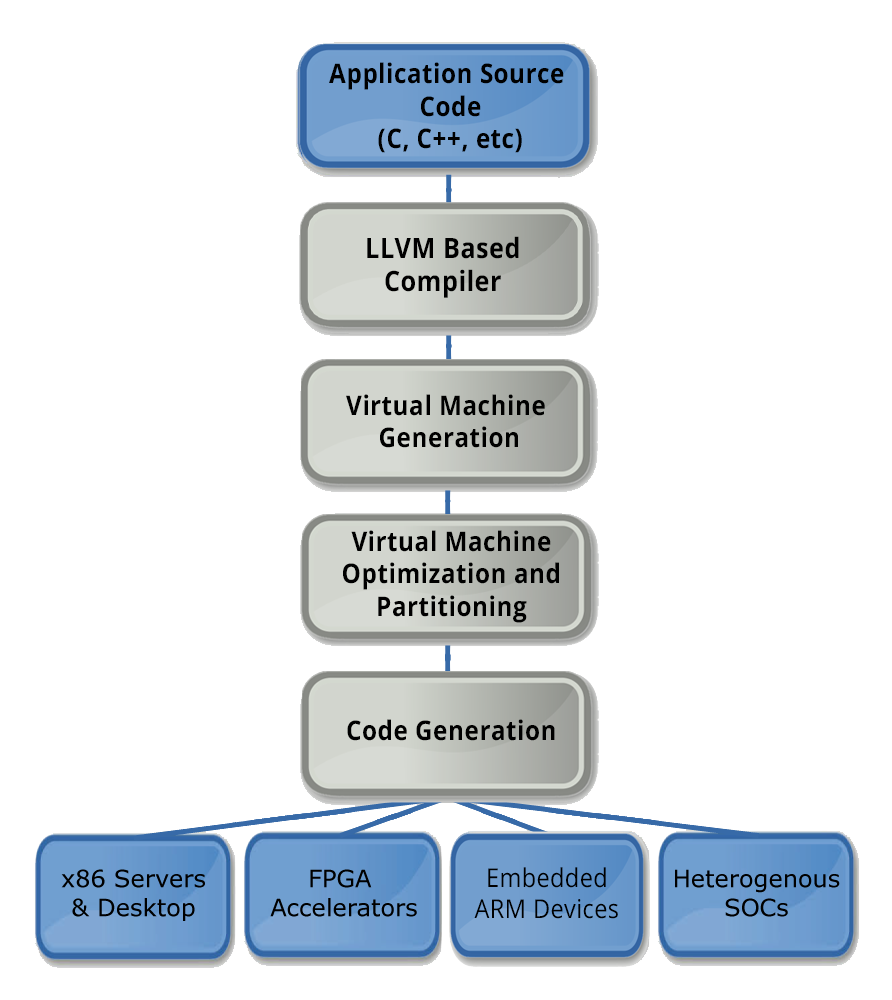

The CacheQ Development FlowThe QCC development platform accepts High Level Language (C/C++/Fortran) as input and through a number of steps generates an optimized, partitioned, and accelerated executable. All of these outputs are supported from the same original source code with no hardware specific languages or pragmas (cuda/opencl/HDL/oneAPI) necessary. The platform supports the generation of multithreaded x86, ARM, RISCV or M1 executables, partitioned x86 + nVidia/AMD GPU kernel accelerators, partitioned x86 + FPGA executables targeting FPGA PCIe attached accelerators, partitioned ARM + FPGA executable targeting FPGA SOCs and partitioned RISCV + FPGA executable targeting FPGA SOCs. Multithreaded executables are compiled to execute on multicore devices. The qcc Development Platform offers a complete suite of analysis tools. Analysis and optimization capabilities include FPGA area estimation, FPGA device selection, FPGA performance estimation, and memory access analysis.

The only multiple vendor, edge and data center, multiple technology heterogeneous acceleration development platform.

The CacheQ Virtual Machine

The CacheQ Virtual Machine is a complete software representation of the application. It supports design analysis, profiling, performance simulation and application partitioning. It enables high bandwidth memory integration. All across multiple platforms.

THe Development Flow

The development flow takes HLL, generates a CQVM, performs analysis and optimization. For multithreading a C++ file is generated and then compiled by the C++ compiler of choice. For FPGA acceleration the design is partitioned and then generates an x86 executable and system Verilog. The system Verilog is processed by FPGA tools to generate a “bitstream”. Even though the system produces RTL the RTL is a representation of the fully pipelined CQVM and not state machine controlled digital logic. The CQVM also supports user-guided partitioning, performance simulation, profiling, memory configuration (size and stripping) and resource estimates. Minor modifications are usually implemented to enhance the performance of the application. These changes can be fully validated in a standard SW development environment.

The same source file can be used to target multicore implementations or FPGA accelerated implementations.